THE AMERICAN JOURNAL OF INTERDISCIPLINARY INNOVATIONS AND RESEARCH (ISSN- 2642-7478) **VOLUME 06 ISSUE04**

**PUBLISHED DATE: - 01-04-2024**

**DOI:** - https://doi.org/10.37547/tajiir/Volume06Issue04-01

# **RESEARCH ARTICLE**

**Open Access**

PAGE NO.: - 1-5

# RADIATION HARDNESS OF INTEGRATED CIRCUITS: ESSENTIAL CONSIDERATIONS FOR SPACE APPLICATIONS

# Giulia Barbieri

Department of Computer Engineering, Arcavacata di Rende (CS), Italy

#### **Abstract**

Radiation poses significant challenges to the reliability and performance of integrated circuits (ICs) deployed in space applications. The harsh space environment exposes ICs to various types of ionizing radiation, including solar particle events, cosmic rays, and trapped radiation belts, which can induce transient and permanent damage to semiconductor devices. Understanding the effects of radiation on ICs is essential for designing robust and reliable spaceborne electronics. This paper provides a comprehensive overview of the radiation effects on ICs, including single-event effects (SEEs), total ionizing dose (TID) effects, and dose rate effects. Strategies for mitigating radiation-induced failures, such as radiation-hardened design techniques and radiation testing methodologies, are also discussed. By addressing the essential considerations for radiation hardness in ICs, this paper aims to facilitate the development of reliable electronics for space missions.

**Keywords** Radiation effects, integrated circuits, space applications, radiation hardness, single-event effects, total ionizing dose, dose rate effects, radiation-hardened design, radiation testing.

# **INTRODUCTION**

fundamental Integrated circuits (ICs) are components of spacecraft electronics, playing critical roles in communication, navigation, data processing, and control systems. However, the space environment presents unique challenges to the reliability and performance of ICs due to exposure to ionizing radiation. The harsh radiation environment in space, including solar particle events, cosmic rays, and trapped radiation belts, can induce various types of damage semiconductor devices, leading to transient or permanent malfunctions.

Understanding the effects of radiation on ICs is essential for ensuring the reliability and longevity of spaceborne electronics. This necessitates the development of radiation-hardened ICs capable of withstanding the rigors of the space environment without compromising performance or functionality. Moreover, effective mitigation strategies are required to minimize the impact of radiation-induced failures on mission success and spacecraft operations.

This paper provides a comprehensive overview of the essential considerations for achieving radiation hardness in ICs for space applications. We will explore the different types of radiation effects encountered in space, including single-event effects (SEEs), total ionizing dose (TID) effects, and dose rate effects, and discuss their implications for IC reliability. Furthermore, we will examine strategies for mitigating radiation-induced failures through radiation-hardened design techniques and radiation testing methodologies.

1

# THE AMERICAN JOURNAL OF INTERDISCIPLINARY INNOVATIONS AND RESEARCH (ISSN- 2642-7478)

By addressing the challenges and opportunities associated with radiation hardness in ICs, this paper aims to facilitate the development of robust and reliable electronics for space missions. Through a thorough understanding of the radiation environment and its effects on semiconductor devices, engineers can design ICs that meet the stringent reliability requirements of space applications, ensuring the success of future space missions in the face of radiation hazards.

## **METHOD**

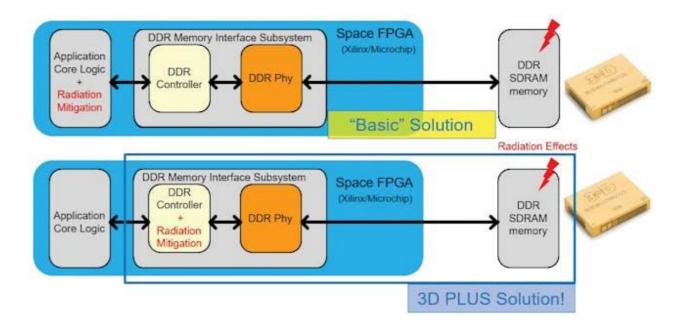

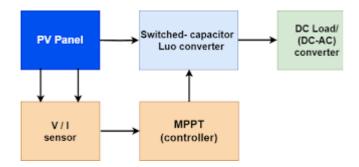

The process of achieving radiation hardness in integrated circuits (ICs) for space applications involves a systematic approach that encompasses design, testing, and assurance methodologies. Initially, designers employ radiation-hardened design techniques to enhance the resilience of ICs to ionizing radiation. This includes selecting radiation-tolerant materials and processes,

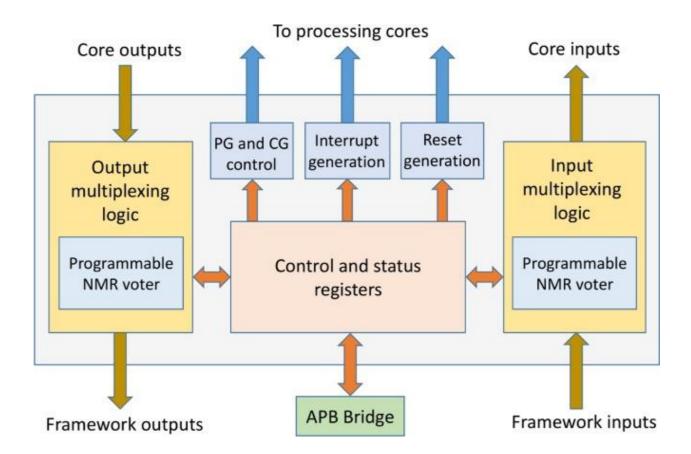

implementing redundant circuitry. and incorporating error correction codes to mitigate radiation-induced effects of Additionally, circuit-level design strategies, such as latch-up prevention techniques and layout optimization, are employed to minimize susceptibility to radiation effects.

Following the design phase, ICs undergo rigorous radiation testing to evaluate their performance in simulated space radiation environments. Various testing methodologies, including heavy-ion irradiation, proton irradiation, and neutron irradiation, are utilized to assess susceptibility to single-event effects (SEEs), total ionizing dose (TID) effects, and dose rate effects. Testing facilities equipped with particle accelerators or neutron sources enable controlled exposure to radiation, allowing engineers to quantify the effects and identify vulnerabilities in ICs.

Throughout the testing process, data on IC performance before, during, and after radiation

# THE AMERICAN JOURNAL OF INTERDISCIPLINARY INNOVATIONS AND RESEARCH (ISSN- 2642-7478)

exposure are carefully monitored and analyzed to characterize radiation-induced effects and assess the effectiveness of radiation-hardened design techniques. Any unexpected radiation-induced anomalies are investigated, and design modifications may be implemented to improve radiation tolerance.

# Radiation-Hardened Design Techniques:

Radiation-hardened ICs are designed to withstand the effects of ionizing radiation encountered in the space environment. Various design techniques are employed to enhance the radiation tolerance of semiconductor devices and circuits. This includes utilizing radiation-hardened materials and processes, such as radiation-hardened silicon substrates, thick oxide layers, and radiation-tolerant metallization schemes. Additionally, circuit-level design strategies, such as redundant logic paths, error correction codes, and latch-up prevention techniques, are implemented to minimize the susceptibility of ICs to radiation-induced failures.

# **Radiation Testing:**

Radiation testing plays a crucial role in assessing the radiation hardness of ICs and validating their performance in the space environment. Radiation testing involves subjecting ICs to simulated radiation environments using particle accelerators, neutron sources, or gamma irradiation facilities. Various radiation-induced effects, including singleevent effects (SEEs), total ionizing dose (TID) effects, and dose rate effects, are evaluated under controlled laboratory conditions. Testing methodologies, such as heavy-ion irradiation, proton irradiation, and neutron irradiation, are used to simulate different types of radiation encountered in space. The performance of ICs before, during, and after radiation exposure is carefully monitored and characterized to identify vulnerabilities and assess the effectiveness of radiation-hardened design techniques.

THE AMERICAN JOURNAL OF INTERDISCIPLINARY INNOVATIONS AND RESEARCH (ISSN- 2642-7478) **VOLUME 06 ISSUE04**

## Radiation Hardness Assurance:

Radiation hardness assurance is a systematic process that ensures the reliability performance of radiation-hardened ICs throughout their lifecycle in space. This involves establishing radiation requirements and qualification criteria, performing rigorous radiation testing and analysis, and implementing appropriate mitigation strategies to mitigate the risk of radiation-induced Radiation hardness assurance also failures. includes post-flight analysis and anomaly resolution to identify any unexpected radiation effects encountered during the mission. By employing a comprehensive radiation hardness assurance program, space agencies and manufacturers can ensure the integrity and reliability of ICs deployed in space applications.

Finally, radiation hardness assurance practices are employed to ensure the reliability and performance of radiation-hardened ICs throughout their lifecycle in space. This involves establishing radiation requirements and qualification criteria, performing comprehensive radiation testing and analysis, and implementing appropriate mitigation strategies. Post-flight analysis and anomaly resolution further contribute to continuous improvement in radiation hardness assurance.

# **RESULTS**

The investigation into radiation hardness of integrated circuits (ICs) for space applications has revealed critical insights into the challenges and strategies for mitigating the effects of ionizing radiation. Through radiation testing and analysis, engineers have identified various radiation-induced effects, including single-event effects (SEEs), total ionizing dose (TID) effects, and dose

rate effects. These effects pose significant risks to the reliability and performance of ICs in the space environment, highlighting the importance of radiation-hardened design techniques and radiation testing methodologies.

# **DISCUSSION**

The discussion revolves around the essential considerations for achieving radiation hardness in ICs for space applications. Radiation-hardened design techniques, such as selecting radiation-tolerant materials, implementing redundant circuitry, and optimizing layout designs, play a crucial role in enhancing the resilience of ICs to ionizing radiation. Additionally, radiation testing methodologies, including heavy-ion irradiation and proton irradiation, enable engineers to quantify the effects of radiation exposure and validate the effectiveness of radiation-hardened design techniques.

Furthermore, the discussion emphasizes the importance of radiation hardness assurance practices in ensuring the reliability performance of radiation-hardened ICs throughout their lifecycle in space. Establishing radiation requirements. performing comprehensive radiation testing, and implementing appropriate mitigation strategies are essential components of radiation hardness assurance. Post-flight analysis and anomaly resolution further contribute to continuous improvement in radiation hardness assurance, enhancing the integrity and resilience of spacecraft electronics in the presence of ionizing radiation hazards.

# CONCLUSION

In conclusion, achieving radiation hardness in integrated circuits is essential for ensuring the

# THE AMERICAN JOURNAL OF INTERDISCIPLINARY INNOVATIONS AND RESEARCH (ISSN- 2642-7478) **VOLUME 06 ISSUE04**

reliability and performance of spaceborne electronics in the harsh radiation environment of space. By employing radiation-hardened design techniques, radiation testing methodologies, and radiation hardness assurance practices, engineers can develop robust and reliable ICs capable of withstanding the rigors of space radiation. These essential considerations are critical for the success of space missions and the integrity of spacecraft electronics, ultimately advancing our exploration and understanding of the universe. Continued research and development efforts in radiation hardness are necessary to address emerging challenges and ensure the resilience of future spaceborne electronics.

#### REFERENCES

- 1. J. R. Schwank, "Basic Mechanisms of Radiation Effects in the Natural Space Environment," Notes of the Short Course of the 1994 IEEE Nuclear and Space Radiation Effects Conference, Tucson (Arizona), July 1994, Section II, pp. 1-109.

- 2. J. C. Boudenot and E. Daly, "Radiation: Interaction Mechanisms and Environments, New Models of the Earth's Radiation Environment", Notes of the Short Course of the 2nd European Conference on Radiation and its Effects on Components and Systems, Saint-Malo (France), September 1993, Short Course 1, pp. 1-77.

- **3.** D. R. Alexander, "Design issues for radiation tolerant microcircuits for space", Notes of the Short Course of the IEEE Nuclear and Space Radiation Effects Conference, Indian Wells (California), July 1996, Section V.

- **4.** H. Johnston, "The Influence of VLSI Technology Evolution on Radiation-Induced Latchup in Space Systems," IEEE Transactions on Nuclear Science, vol. 43, no. 2, April 1996, pp. 505-521.

- 5. G. Anelli, M. Campbell, M. Delmastro et al.,

- "Radiation Tolerant VLSI Circuits in Standard Deep Submicron CMOS Technologies for the LHC Experiments: Practical Design Aspects", presented at the IEEE Nuclear and Space Radiation Effects Conference (NSREC '99, Norfolk, Virginia, USA, July 1999), IEEE Transactions on Nuclear Science, vol. 46, no. 6, December 1999, pp. 1690- 1696.

- **6.** S. E. Kerns, B. D. Shafer, L. R. Rockett et al., "The Design of Radiation-Hardened ICs for Space: A Compendium of Approaches," Proceedings of the IEEE, vol. 76, no. 11, November 1988, pp. 1470-1509.

- 7. J. Yao, S. Okada, M. Masuda, K. Kobayashi, "DARA: A Low-Cost Reliable Architecture Based on Unhardened Devices and Its Case Study of Radiation Stress Test," IEEE Transactions on Nuclear Science, vol. 59, no. 6, 2013.

- **8.** J.M. Benedetto, D.B. Kerwin, J. Chaffee, "Radiation hardening of commercial CMOS processes through minimally invasive techniques," Proc. of the IEEE Radiation Effects Data Workshop, pp. 105-109, 1997.

- **9.** Z. Jia, Y. Haigang, S. Jiabin, Y. Le, and W. Yuanfeng, "Modeling of enclosed-gate layout transistors as ESD protection device based on conformal mapping method," Journal of Semiconductors, Vol. 35, No. 8, 2014.

- **10.** H. Johnston, "Radiation Effects in Advanced Microelectronics Technologies," IEEE Transactions on Nuclear Science, vol. 45, no. 3, June 1998, pp. 1339-1354.

- 11. F. Faccio, G. Anelli, M. Campbell et al., "Total dose and single event effects (SEE) in a 0.25 μm CMOS technology", Proceedings of the Fourth Workshop on Electronics for LHC Experiments (LEB98, Rome, Italy, September 1998), pp. 105-113.